# 1200/600/300/200 DPI High-Speed Photodiode Array

# Description

The NOP12810 photodiode array (PDA) provides selectable 1200, 600, 300 and 200 dot per inch (dpi) resolution. The sensor contains an on-chip output amplifier, internal power-down capability and parallel transfer features that are uniquely combined with advanced active-pixel-sensor technology. Applications for the photodiode sensor array include currency verification, bar code scanning and industrial process automation equipment.

#### **Features**

- 1200, 600, 300 and 200 dpi Selectable Resolutions

- 696, 348, 174 or 116 Image Sensor Elements (pixels)

- 21.15 μm (1200 dpi) Pixel Center-to-Center Spacing

- On-chip Amplifier

- Single 3.3 V Power Supply

- 3.3 V Input Clocks and Control Signals

- 8.0 MHz Maximum Pixel Rate

- Parallel Integration and Transfer Operations

- Automatic Power-down of Internal Circuitry

- High Sensitivity

- Low Power

- Low Noise

- This is a Pb-Free Device

# **Applications**

- Currency Verification

- Document Scanning

- Barcode Scanning

- Process Automation Equipment

# ON Semiconductor®

http://onsemi.com

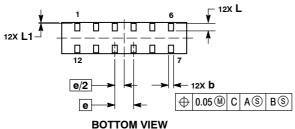

OLCC12 CL SUFFIX CASE 755AA

#### **MARKING DIAGRAM**

(Bottom View of Package)

XXXXXXXX = Specific Device Code

A = Assembly Location

Y = Year W = Work Week

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

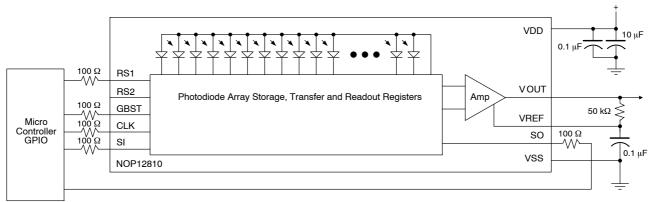

**Figure 1. Typical Application Circuit**

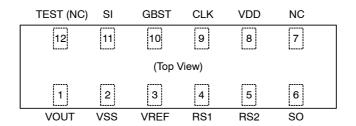

Figure 2. Pinout Configuration

# **Table 1. PIN FUNCTION DESCRIPTION**

| Pin | Pin Name  | Description                                                                                                                              |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VOUT      | Analog video output signal                                                                                                               |

| 2   | VSS       | Ground                                                                                                                                   |

| 3   | VREF      | Input reference voltage for the differential amplifier driving VOUT, sets the output reset (dark) voltage level                          |

| 4   | RS1       | Selects the 1200, 600, 300 or 200 dpi resolution mode                                                                                    |

| 5   | RS2 (NC)  | Has no functionality, this pad should be left unconnected                                                                                |

| 6   | SO        | End-of-scan output pulse used to drive the start pulse (SI) input of the next sensor chip in a module                                    |

| 7   | NC        | No connect, this pad should be left unconnected                                                                                          |

| 8   | VDD       | +3.3 V power supply                                                                                                                      |

| 9   | CLK       | Clock input for the shift register                                                                                                       |

| 10  | GBST      | Global start pulse initializes the start inputs of all sensor chips in a module and starts the scanning process of the first sensor chip |

| 11  | SI        | Start pulse, input to start a line scan                                                                                                  |

| 12  | TEST (NC) | Test pad used during wafer sort, this pad should be left unconnected                                                                     |

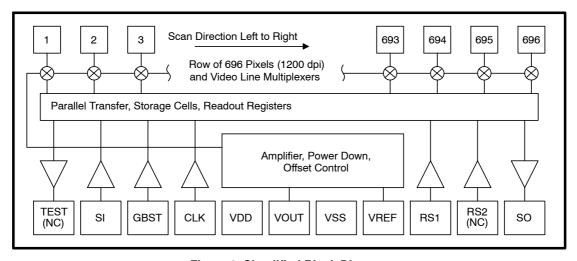

Figure 3. Simplified Block Diagram

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Parameter                                        | Symbol             | Value                                        | Unit |

|--------------------------------------------------|--------------------|----------------------------------------------|------|

| Power supply voltage                             | V <sub>DD</sub>    | 4                                            | V    |

| Input voltage range for CLK, SI, GBST, RS1, VREF | V <sub>in</sub>    | V <sub>SS</sub> -0.5 to V <sub>DD</sub> +0.5 | V    |

| Storage Temperature                              | T <sub>STG</sub>   | –25 to 75                                    | °C   |

| Storage Humidity, Non-Condensing                 | H <sub>STG</sub>   | 10 to 90                                     | %    |

| ESD Capability, Human Body Model (Note 1)        | ESD <sub>HBM</sub> | 2500                                         | V    |

| ESD Capability, Machine Model (Note 1)           | ESD <sub>MM</sub>  | 250                                          | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per EIA/JESD22-A114

ESD Machine Model tested per EIA/JESD22-A115

Latchup Current Maximum Rating: ≤ 100 mA per JEDEC standard: JESD78

Table 3. RECOMMENDED OPERATING RANGES (Unless otherwise specified, these specifications apply T<sub>A</sub> = 25°C)

| Parameter                                                     | Symbol               | Min                   | Тур | Max                   | Unit |

|---------------------------------------------------------------|----------------------|-----------------------|-----|-----------------------|------|

| Power supply voltage                                          | $V_{DD}$             | 3.1                   | 3.3 | 3.5                   | V    |

| Power supply current, initialization – first 100 clock cycles | I <sub>DD_INIT</sub> |                       | 5.8 |                       | mA   |

| Power supply current, integration and transfer mode           | I <sub>DD_OPER</sub> |                       | 40  |                       | mA   |

| Power supply current, idle mode, still integrating            | I <sub>DD_IDLE</sub> |                       | 3.2 |                       | mA   |

| Low level input voltage for CLK, SI, GBST, RS1                | V <sub>IL</sub>      | V <sub>SS</sub> – 0.5 |     | 0.6                   | V    |

| High level input voltage for CLK, SI, GBST, RS1               | V <sub>IH</sub>      | 2.8                   |     | V <sub>DD</sub> + 0.1 | V    |

| Reference voltage                                             | $V_{REF}$            | 1.1                   | 1.2 | 1.3                   | V    |

| Clock frequency                                               | f                    | 0.5                   | 8.0 | 8.0                   | MHz  |

| Pixel rate (Note 2)                                           | $P_{R}$              | 0.5                   | 8.0 | 8.0                   | MHz  |

| Integration time (line scan rate) (Note 3)                    | T <sub>int</sub>     |                       |     | 99.5                  | μs   |

| Resistive load on VOUT                                        | R <sub>L</sub>       | 50                    | 50  |                       | kΩ   |

| Capacitive load on VOUT                                       | C <sub>L</sub>       |                       |     | 150                   | pF   |

| Operating Temperature                                         | T <sub>op</sub>      | -10                   |     | 50                    | °C   |

| Operating Humidity, Non-Condensing                            | H <sub>op</sub>      | 10                    |     | 85                    | %    |

<sup>2.</sup> One pixel is clocked out for every clock cycle.

**Table 4. PHYSICAL SPECIFICATIONS**

| Parameter                        | Symbol               | Тур    | Unit |

|----------------------------------|----------------------|--------|------|

| Number of pixels, 1200 dpi       | P <sub>n_1200</sub>  | 696    |      |

| Number of pixels, 600 dpi        | P <sub>n_600</sub>   | 348    |      |

| Number of pixels, 300 dpi        | P <sub>n_300</sub>   | 174    |      |

| Number of pixels, 200 dpi        | P <sub>n_200</sub>   | 116    |      |

| Pixel-to-pixel spacing, 1200 dpi | D <sub>pp_1200</sub> | 21.15  | μm   |

| Pixel-to-pixel spacing, 600 dpi  | D <sub>pp_600</sub>  | 42.30  | μm   |

| Pixel-to-pixel spacing, 300 dpi  | D <sub>pp_300</sub>  | 84.60  | μm   |

| Pixel-to-pixel spacing, 200 dpi  | D <sub>pp_200</sub>  | 126.90 | μm   |

<sup>3.</sup> Tint is the integration time of a single sensor and is the time between two start pulses. The minimum integration time is the time it takes to clock out 100 inactive pixels and 696 active pixels for the 1200 dpi mode, 100 inactive pixels and 348 active pixels for the 600 dpi mode, 100 inactive pixels and 174 active pixels for the 300 dpi mode or 100 inactive pixels and 116 active pixels for the 200 dpi mode, at a given frequency.

Table 5. SWITCHING CHARACTERISTICS (Unless otherwise specified, these specifications apply  $T_A = 25$ °C) (Note 4)

| Parameter                        | Symbol              | Min | Тур  | Max  | Unit |

|----------------------------------|---------------------|-----|------|------|------|

| CLK clock period (Note 5)        | t <sub>o</sub>      |     | 125  | 2000 | ns   |

| CLK pulse width (Note 5)         | t <sub>w</sub>      |     | 62.5 |      | ns   |

| CLK duty cycle (Note 6)          | DC <sub>CLK</sub>   | 45  | 50   | 55   | %    |

| GBST setup time (Notes 5, 7)     | t <sub>su</sub>     | 20  |      |      | ns   |

| GBST hold time (Notes 5, 7)      | t <sub>h</sub>      | 25  |      |      | ns   |

| CLK rise time (Notes 5, 8)       | t <sub>r_CLK</sub>  |     |      | 62.5 | ns   |

| CLK fall time (Notes 5, 8)       | t <sub>f_CLK</sub>  |     |      | 62.5 | ns   |

| GBST rise time (Notes 5, 8)      | t <sub>r_GBST</sub> |     |      | 62.5 | ns   |

| GBST fall time (Notes 5, 8)      | t <sub>f_GBST</sub> |     |      | 62.5 | ns   |

| Pixel output timing, CLK = 8 MHz | TS                  | 75  |      |      | ns   |

| Pixel output rise time (Note 9)  | P <sub>rt</sub>     |     | TBD  |      | ns   |

- 4. Refer to Figure 4 through Figure 6 for more information on AC characteristics.

- 5. Assuming a 50% duty cycle.

- 6. Defined as the ratio of the positive duration of the clock to its period.

- 7. The shift register loads on the falling edge of CLK, therefore setup and hold times (tsu, th) are needed to prevent loading of multiple start pulses. This would occur if GBST remains high during two fallings edges of the CLK signal. See Figure 4.

- 8. Clock rise time should match clock fall time.

- 9. Pixel output rise time measured at 8 MHz with 150 pF and 50  $k\Omega$  load to ground with the output at saturation.

Table 6. ELECTRO-OPTICAL CHARACTERISTICS TEST CONDITIONS

| Parameter                              | Symbol                | Value | Unit |

|----------------------------------------|-----------------------|-------|------|

| Power supply voltage                   | V <sub>DD</sub>       | 3.3   | V    |

| Reference voltage                      | V <sub>REF</sub>      | 1.2   | V    |

| Clock frequency                        | f                     | 8.0   | MHz  |

| Clock pulse duty cycle                 | DC <sub>CP</sub>      | 50    | %    |

| Integration time, 1200 dpi             | T <sub>int_1200</sub> | 99.5  | μs   |

| Integration time, 600 dpi              | T <sub>int_600</sub>  | 56.0  | μs   |

| Integration time, 300 dpi              | T <sub>int_300</sub>  | 34.25 | μs   |

| Integration time, 200 dpi              | T <sub>int_200</sub>  | 27.0  | μs   |

| Resistive load on VOUT (Note 10)       | R <sub>L</sub>        | 50    | kΩ   |

| Capacitive load on VOUT (Note 11)      | CL                    | 150   | pF   |

| Average output voltage swing (Note 12) | V <sub>avg</sub>      | 1.0   | V    |

| LED peak wavelength (Note 13)          | λρ                    | 550   | nm   |

| Operating Temperature                  | T <sub>op</sub>       | 25    | °C   |

<sup>10.</sup> Resistive load connected between VOUT and VREF. VREF is typically has a lower noise level than VSS.

<sup>11.</sup> Capacitive load connected between VOUT and VSS.

<sup>12.</sup> The average output voltage Vavg is defined as the voltage difference between the average pixel level in the light and the average pixel level in the dark. It should be adjusted to approximately 1.0 V, unless stated otherwise.

<sup>13.</sup> A linear array of uniform green LEDs acts as the light source for measurements requiring illumination, unless otherwise stated.

#### Table 7. ELECTRO-OPTICAL CHARACTERISTICS

(Unless otherwise specified, these specifications were achieved with the test conditions defined in Table 6)

| Parameter                                              | Symbol              | Min                      | Тур       | Max                      | Unit                 |

|--------------------------------------------------------|---------------------|--------------------------|-----------|--------------------------|----------------------|

| Dark output voltage (Note 14)                          | $V_d$               | V <sub>REF</sub> – 0.150 | $V_{REF}$ | V <sub>REF</sub> + 0.150 | V                    |

| Dark output non-uniformity (Note 15)                   | U <sub>d</sub>      | 0                        |           | 100                      | mV                   |

| Photo-response non-uniformity (Note 16)                | U <sub>p</sub>      | -15                      |           | 15                       | %                    |

| Adjacent pixel photo-response non-uniformity (Note 17) | U <sub>padj</sub>   | 0                        |           | 15                       | %                    |

| Saturation voltage (Note 18)                           | V <sub>Sat</sub>    |                          | 1.2       |                          | V                    |

| Sensitivity, 1200 dpi (Note 19)                        | S <sub>V_1200</sub> |                          | 850       |                          | V/μJ/cm <sup>2</sup> |

| Sensitivity, 600 dpi (Note 19)                         | S <sub>V_600</sub>  |                          | TBD       |                          | V/μJ/cm <sup>2</sup> |

| Sensitivity, 300 dpi (Note 19)                         | S <sub>V_300</sub>  |                          | TBD       |                          | V/μJ/cm <sup>2</sup> |

| Sensitivity, 200 dpi (Note 19)                         | S <sub>V_200</sub>  |                          | TBD       |                          | V/μJ/cm <sup>2</sup> |

| Photo-response linearity (Note 20)                     | PRL                 | 99                       |           | 107                      | %                    |

| Individual rms pixel noise, 1200 dpi (Note 21)         | P_noise             | 0                        | 3         | 4.5                      | mV                   |

| Image lag (chip average) (Note 22)                     | IL                  |                          |           | 1                        | %                    |

<sup>14.</sup> Vd is the average dark output level and represents the offset level of the video output in the dark. The dark level is set by VREF and is recommended to be 1.2 V for optimal module operation.

15. Ud = Vdmax - Vdmin, where

Vdmax is the maximum pixel output voltage in the dark

Vdmin is the minimum pixel output voltage in the dark

In the 1200 dpi mode, dark output non-uniformity is tested at 4 ms.

16. Up = [(Vpmax - Vpavg)/Vpavg] x 100%, or [Vpavg - Vpmin)/Vpavg] x 100%, whichever is greater, where

Vpmax is the maximum pixel voltage of any pixel at full bright

Vpmin is the minimum pixel voltage of any pixel at full bright

Vpavg is average output voltage of all pixels at full bright.

17. Upadj = MAX [ |  $(Vp(n) - Vp(n+1) | / Vpavg] \times 100\%$ , where

Upadj is the nonuniformity in percent between adjacent pixels for a bright background

Vp(n) is the pixel output voltage of pixel n at full bright.

- 18. VSat is defined as the maximum video output voltage swing measured from the dark level to the saturation level. It is measured by using the module LED light source with the module imaging a uniform white target. The LED light level is increased until the output voltage no longer increases with an increase in the LED brightness.

- 19. Sv is defined as the slope of the Vpavg vs. Exposure curve. Sensitivity uniformity is nominally better than ±10% die-to-die.

- 20. PRL = ((Vratio Tratio) / Tratio) x 100%, where

Vratio = (Vavg3 - Vavg1) / (Vavg2 - Vavg1)

Tratio = (Tint3 - Tint1) / (Tint2 - Tint1)

Tint1 is the integration time needed to get a Vavg1 of about 0.1 V

Tint2 is the integration time needed to get a Vavg2 of about 0.5 V

Tint3 is the integration time needed to get a Vavg3 of about 0.9 V

- A specification limit of 5% for this test method is a tighter spec than  $\pm 5\%$  deviation from a best fit line. Linearity is specified within the range of the saturation voltage.

- 21. Individual rms pixel noise is defined as the standard deviation of each pixel in the dark. This can also be considered output referred noise as it is measured at the sensor output.

- 22. Image lag is defined as taking two subsequent CIS reads where the first readout occurs when the sensor is illuminated such that the imager output voltage is in saturation and the second readout occurs with zero irradiance falling on the sensor.

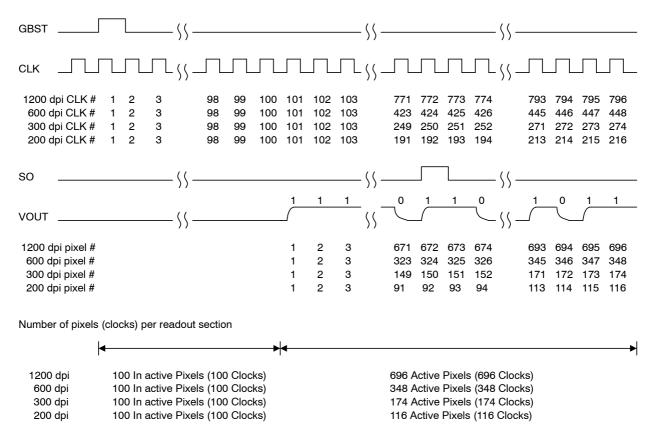

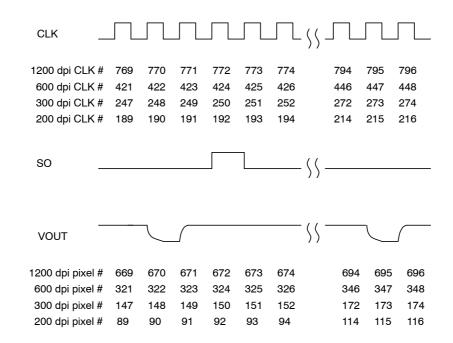

Figure 4. Overall Timing Diagram for 1200/600/300/200 dpi Modes

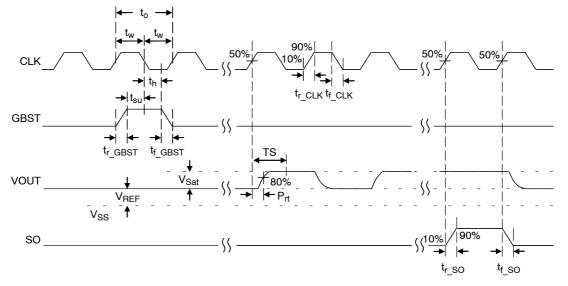

Figure 5. Rise and Fall Times for 1200/600/300/200 dpi Modes

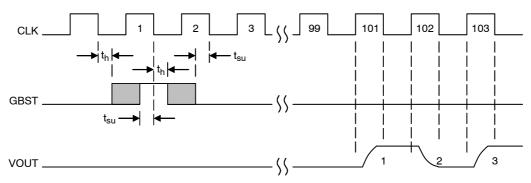

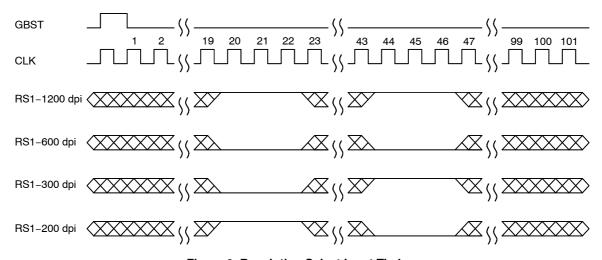

Figure 6. Timing of GBST-to-First Pixel for 1200/600/300/200 dpi Modes

Figure 7. Timing of SI/SO Clock for 1200/600/300/200 dpi Modes

# **Description of Operation**

# **Functional Description**

The NOP12810 photodiode array has selectable 1200, 600, 300 and 200 dpi resolution. The sensor contains an on-chip output amplifier, automatic power-down circuitry and parallel transfer features that are uniquely combined with advanced active-pixel-sensor technology. The image photodiode array is designed to be part of an image acquisition system including the necessary optical lens as illustrated in Figure 1.

Figure 3 is a block diagram of the sensor. Each sensor consists of 696 active pixels, their associated multiplexing switches, buffers and an output amplifier circuit with power down. The pixel–to–pixel spacing is  $21.15 \mu m$ .

There are a number of features incorporated into the NOP12810 which improve the sensor's performance.

# **Active Pixel Technology**

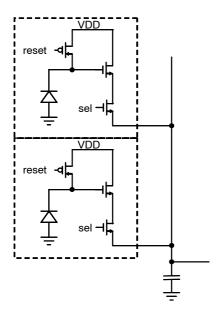

Active pixel technology supplements the primary photodiode sensor element with additional transistors which condition, amplify and buffer the original signal. Figure 8 illustrates a pair of active pixel cells connected to the internal scan line.

Figure 8. Active Pixel Cell Architecture

#### Pixel-to-Pixel Offset Cancellation Circuit

The sensor employs a pixel-to-pixel offset cancellation circuit, which reduces the fixed pattern noise (FPN) and amplifier offsets. This innovative circuit design greatly improves the optical linearity and low noise sensitivity.

# Parallel Integrate, Hold and Transfer

The sensor has a parallel integrate, transfer and hold feature which allows the sensor to scan data out while photon integration is taking place. These features are approached through the use of an integrate—and—hold cell

located at each pixel site. Each pixel's charge is read from its storage site as the shift register sequentially selects each pixel and transfers each pixel's charge onto a common video line.

#### Scan Initiation Inputs GBST and SI

The sensor has two scan initiation inputs, the global start pulse (GBST) and the start pulse (SI) which are compatible with standard 3.3 V CMOS signal levels. The scan cycle starts when GBST is captured on the falling edge of the clock input (CLK). During the first 100 clock cycles following a GBST pulse, all the pixels cycle through their pre–scan initialization process that reduces FPN and reset noise.

SI selects when an individual sensor is selected. By permanently asserting the SI pin, the scanning sequence is properly initialized. The sensor clocks out 100 inactive pixels before accessing its first active pixel. During these 100 clock cycles, the sensor cycles through the pre–scan initialization process. After initialization, the sensor starts its read cycle with its first–active pixel appearing on the 100th clock cycle.

#### **Power Saving Mode**

The sensor incorporates an internal power–saving feature. When the SI pin of a particular sensor is selected for read out, the sensor powers up the output amplifier and then powers it down when the read scan is completed.

# **Common Reference Voltage**

The sensor has an input bias control (VREF), which serves as an offset voltage reference for the output amplifier. In multiple chip operation, the VREF inputs are tied together such that each sensor references the same bias level.

# Selectable Resolutions of 400, 300, 200 and 100 dpi

The select resolution input (RS1) is used to select between 1200, 600, 300 and 200 dpi modes.

- For 1200 dpi, the RS1 input is held high (Vdd)

- For 600 dpi, the RS1 input is held low (Vss)

- For 300 dpi, the RS1 input is held low for clocks 20, 21 and 22 and then high for clocks 44, 45 and 46

- For 200 dpi, the RS1 input is held high for clocks 20, 21 and 22 and then low for clocks 44, 45 and 46

In 1200 dpi mode, all 696 pixels are clocked out. In the 600 dpi mode, pixels 1 and 2 are combined, 3 and 4 are combined and so on up to pixels 695 and 696 being combined. This will give a net pixel count of 348 pixels. Similarly, in 300 dpi mode, pixels 1, 2, 3, and 4 are combined; pixels 5, 6, 7, and 8 are combined and so on up to pixels 693, 694, 695, and 696 being combined. In 200 dpi mode, pixels 1, 2, 3, 4, 5 and 6 are combined, pixels 7, 8, 9, 10, 11 and 12 are combined and so on up to pixels 691, 692, 693, 694, 695 and 696 being combined.

In the 600 dpi mode, one half of the pixel amplifiers and one half of the scanning register are disabled when compared to the 1200 dpi mode. As a result, sensitivity in the 600 dpi mode will be twice that of the 1200 dpi mode. The 600 dpi readout time will be approximately half of the 1200 dpi readout time. Similarly, in 300 dpi mode three quarters of the pixel amplifiers and three quarters of the scanning registers are then disabled. As a result, sensitivity in the 300 dpi mode will be four times that of the 1200 dpi mode. The 300 dpi readout time will be approximately a quarter of the 1200 dpi readout time. In the 200 dpi mode five sixths of the pixel amplifiers and five sixths of the scanning registers are disabled. Sensitivity in 200 dpi mode is six times the sensitivity in 1200 dpi mode. The 200 dpi readout time will be approximately one sixth of the 1200 dpi readout time. Unlike a CCD array, the 1200 dpi, 600 dpi, 300 dpi and 200 dpi modes all operate at the same clock frequency.

# **Timing**

Figure 4 shows the initialization of the sensor for the 1200 dpi, 600 dpi, 300 dpi and 200 dpi modes. The sensor will operate with 100 inactive pixels being clocked out before its first active pixel is clocked out.

Figure 4 and Figure 5 detail the timing of the CLK, GBST, OUT, and SI/SO signals in further detail, they have the same timing requirements for the 1200, 600, 300 and 200 dpi modes. The rise and fall times are listed in Table 5. In Figure 6, note that clock 100 is the first active pixel, as the first 100 clocks produce dummy pixels (the output of the first 100 clocks should not be used for any purpose such as black level clamping).

Figure 7 shows the timing of the SO signal for the 1200 dpi, 600 dpi, 300 dpi and 200 dpi modes, which corresponds with the 672nd pixel for the 1200 dpi mode, 324th pixel for the 600 dpi mode, the 150th pixel for the 300 dpi mode and 92nd pixel for 200 dpi mode. The sensor's SO signal can be used to determine when the end of the scan is reached. The last active pixel is the 696th pixel for the 1200 dpi mode, 348th pixel for the 600 dpi mode, the 174th pixel for the 300 dpi mode and 116th pixel for the 200 dpi mode.

Figure 9. Resolution Select Input Timing

#### **ORDERING INFORMATION**

| Device        | Package             | Temperature Range | Shipping <sup>†</sup> |

|---------------|---------------------|-------------------|-----------------------|

| NOP12810CLTAG | OLCC12<br>(Pb-Free) | −40°C to +85°C    | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

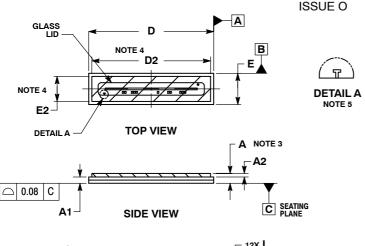

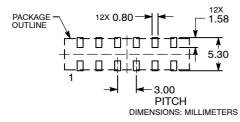

#### PACKAGE DIMENSIONS

#### OLCC12 20x5, 3.0P

CASE 755AA ISSUE O

# RECOMMENDED SOLDERING FOOTPRINT\*

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS.

- 3. DIMENSION A INCLUDES THE PACKAGE BODY AND LID BUT DOES NOT INCLUDE HEATSINKS OR OTHER ATTACHED FEATURES.

- 4. THE GLASS LID DEFINED BY DIMENSIONS D2 AND E2 MUST BE LOCATED WITHIN DIMENSIONS D AND E.

- PIN ONE INDICATOR SHALL BE AS SHOWN IN THIS LOCATION.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 1.37        | 1.77  |  |

| A1  | 1.00        | REF   |  |

| A2  | 0.50        | REF   |  |

| b   | 0.75        | 0.85  |  |

| D   | 19.90       | 20.10 |  |

| D2  | 19.00 REF   |       |  |

| E   | 4.90        | 5.10  |  |

| E2  | 4.00        | REF   |  |

| е   | 3.00 BSC    |       |  |

| L   | 1.15        | 1.25  |  |

| L1  | 0.10        | 0.20  |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada

Fax: 303-675-2173 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative